# **IPM Photocoupler**

## **Product Description**

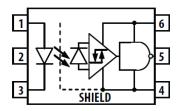

The EMD2A481 fast speed photocoupler contains a LED and photo detector with built-in Schmitt trigger to provide logic-compatible waveforms, eliminating the need for additional wave shaping. The totem pole output eliminates the need for a pull up resistor and allows for direct drive Intelligent Power Module or gate drive. Minimized propagation delay difference between devices makes these optocouplers excellent solutions for improving inverter efficiency through reduced switching dead time.

#### **Applications**

- IPM Interface Isolation

- Isolated IGBT/MOSFET Gate Drive

- AC and Brushless DC Motor Drives

- Industrial Inverters

#### **Features**

- Totem pole output inverter logic type

- Truth Table Guaranteed: VCC from 4.5V to 30V

- Performance Specified for Common IPM Applications Over Industrial Temperature Range.

- Short Maximum Propagation Delays

- Minimized Pulse Width Distortion (PWD)

- Very High Common Mode Rejection (CMR)

- Hysteresis

- Data rate: 5Mbps (typ.)

#### Safety approved

- UL1577 recognized with 3750 Vrms for 1 minute for EMD2A481-SK and 5000 Vrms for 1 minute for EMD2A481-SL Certificate No. E529603

- IEC/EN/DIN EN 60747-5-5 Approved

VIORM = 891 Vpeak for EMD2A481-SK

VIORM = 1140 Vpeak for EMD2A481-SL

Certificate No. 40055846

- CQC approved: GB4943.1-2011Certificate No. CQC22001358589

| SCHEMATIC                                                                                                                                                           | PIN DEFINITION                                         | PACKAGE |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------|

| PULSE GEN.  t <sub>1</sub> = t <sub>2</sub> = 5 ns f = 100 kHz 10% DUTY CYCLE V <sub>0</sub> = 5V Z <sub>0</sub> = 50Ω  NODE  R <sub>1</sub> 120 pF  *0.1 μF BYPASS | 1.Anode<br>2.NC<br>3.Cathode<br>4.GND<br>5.VO<br>6.Vcc |         |

Publication Date: Mar. 2024 Revision: 1.0 1/12

## **Connection Diagram**

#### **Order Information**

EMD2A481-00S###%FR1

EMD2A Photo coupler product series

481 Part Number

00 Internal control Code

S### SK06: LSOP-6 Package 7mm clearance

SL06: LSOP-6 Package 8mm clearance

% E: RoHS & Halogen free package with VDE

N: RoHS & Halogen free package

F -40 to 110°C temperature rating

R1 Packing in Tape & Reel

## Order, Mark & Packing Information

| Package | Product ID                                 |           | Mark                                                           | Packing       |

|---------|--------------------------------------------|-----------|----------------------------------------------------------------|---------------|

|         | EMD2A481-00SK06EFR1<br>EMD2A481-00SL06EFR1 | 481<br>HV | E : ESMT<br>YY : Date code (Year)<br>WW : Date code (Week)     | Tape &        |

| LSOP-6  | EMD2A481-00SK06NFR1<br>EMD2A481-00SL06NFR1 | 481<br>H  | 481 : Part Number H : Internal Tracking Code V : VDE ID Option | Reel<br>3Kpcs |

Publication Date: Mar. 2024 Revision: 1.0 **2/12**

## IEC/EN/DIN EN 60747-5-5 Insulation Characteristics

| Description                                                               | Symbol     | EMD2A481-SK | EMD2A481-SL | Unit           |  |

|---------------------------------------------------------------------------|------------|-------------|-------------|----------------|--|

| Climatic Classification                                                   |            | 55/100/21   | 55/100/21   |                |  |

| Pollution Degree (DIN VDE 0110/1.89)                                      |            | 2           | 2           |                |  |

| Maximum Working Insulation Voltage                                        | Viorm      | 891         | 1140        | Vpeak          |  |

| Input to Output Test Voltage, Method b (Note 1)                           |            |             |             |                |  |

| VIORM x 1.875=Vpr, 100% Production Test                                   | VPR        | 1671        | 2137        | Vpeak          |  |

| With tm=1sec, Partial discharge < 5pC                                     |            |             |             |                |  |

| Input to Output Test Voltage, Method a (Note 1)                           |            |             |             |                |  |

| VIORM x 1.6=Vpr, 100% Production Test                                     | VPR        | 1426        | 1824        | Vpeak          |  |

| With t <sub>m</sub> =10sec, Partial discharge < 5pC                       |            |             |             |                |  |

| Highest Allowable Overvoltage                                             | VIOTM      | 6000        | 8000        | Vpeak          |  |

| (Transient Overvoltage tini = 60sec)                                      | VIOIM      | 8000        | 8000        | <b>V</b> peak  |  |

| Safety-limiting values – maximum values allowed in the event of a failure |            |             |             |                |  |

| Case Temperature                                                          | Ts         | 175         | 175         | ${\mathcal C}$ |  |

| Input Current                                                             | IS, INPUT  | 150         | 150         | mA             |  |

| Output Power                                                              | Ps, оитрит | 600         | 600         | mW             |  |

| Insulation Resistance at TS, V10 = 500 V                                  | Rs         | >109        | >109        | Ω              |  |

Note 1: Refer to the optocoupler section of the Isolation and Control Components Designer's Catalog, under Product Safety Regulations section, (IEC/EN/DIN EN 60747-5-5) for a detailed description of Method a and Method b partial discharge test profiles.

These optocouplers are suitable for "safe electrical isolation" only within the safety limit data. Maintenance of the safety data shall be ensured by means of protective circuits. Surface mount classification is Class A accordance with CECC 00802.

## **Insulation and Safety-Related Specifications**

| Parameter                                        | Symbol  | EMI    | D2A    | Unit  | Conditions                                                                            |

|--------------------------------------------------|---------|--------|--------|-------|---------------------------------------------------------------------------------------|

| raidiffelei                                      | Symbol  | 481-SK | 481-SL | Offin | Conditions                                                                            |

| Minimum External Air Gap (External               | 1 (101) | 7.0    | 8.0    |       | Measured from input terminals to output                                               |

| Clearance)                                       | L(101)  | 7.0    | 6.0    | mm    | terminals, shortest distance through air.                                             |

| Minimum External Tracking (External Creepage)    | L(102)  | 8.0    | 8.0    | mm    | Measured from input terminals to output terminals, shortest distance path along body. |

| Tracking Resistance (Comparative Tracking Index) | CTI     | >175   | >175   | >     | DIN IEC 112/VDE 0303 Part 1.                                                          |

Publication Date: Mar. 2024

Revision: 1.0 3/12

Elite Semiconductor Microelectronics Technology Inc.

#### Truth Table

| LED | Vcc-Vss (Turn-ON) |

|-----|-------------------|

| LED | OUT               |

| ON  | L                 |

| OFF | Н                 |

Note 2: A 0.1µF bypass capacitor must be connected between Pin 4 and 6.

## Absolute Maximum Ratings (Ta = 25°C unless otherwise specified)

| Parameter                       | Symbol | Min  | Max | Unit |

|---------------------------------|--------|------|-----|------|

| Storage Temperature             | Tstg   | -55  | 125 | °C   |

| Operating Temperature           | Topr   | -40  | 110 | °C   |

| Output IC Junction Temperature  | TJ     | -    | 125 | °C   |

| Average Forward Input Current   | IF     | -    | 20  | mA   |

| Reverse Input Voltage           | VR     | -    | 5   | V    |

| Output Collector Current        | IO     |      | 50  | mA   |

| Supply Voltage                  | VCC    | 0    | 35  | V    |

| Output Collector Voltage        | VO     | -0.5 | Vcc | V    |

| Total Package Power Dissipation | PT     | -    | 145 | mW   |

| Lead Solder Temperature         | Tsol   | -    | 260 | °C   |

Note 3: A ceramic capacitor (0.1 µF) should be connected between pin 6 and pin 4 to stabilize the operation of a high gain linear amplifier. Otherwise, this Photocoupler may not switch properly. The bypass capacitor should be placed within 1 cm of each pin.

#### **Recommended Operation Condition**

| Parameter                       | Symbol              | Min | Max | Unit |

|---------------------------------|---------------------|-----|-----|------|

| Operating Temperature           | T <sub>A</sub>      | -40 | 110 | °C   |

| Supply Voltage                  | Vcc                 | 4.5 | 30  | ٧    |

| Input Current (ON)<br>(Note 4)  | I <sub>F(ON)</sub>  | 1.6 | 5   | mA   |

| Input Voltage (OFF)<br>(Note 5) | V <sub>F(OFF)</sub> |     | 0.8 | ٧    |

Note 4: Detector requires a VCC of 4.5 V or higher for stable operation as output might be unstable if VCC is lower than 4.5 V. Be sure to check the power ON/OFF operation other than the supply current.

Note 5: The initial switching threshold is 1.6 mA or less. It is recommended that 2.2 mA be used to permit at least a 20% LED degradation guard band.

Publication Date: Mar. 2024 Revision: 1.0 4/12

#### **Electrical Characteristics**

All Typical values at  $T_A$  = 25°C, unless otherwise specified; all minimum and maximum specifications are at recommended operating condition.

| Parameter                                        | Symbol  | Min         | Тур          | Max        | Unit  | Test Condition                    |

|--------------------------------------------------|---------|-------------|--------------|------------|-------|-----------------------------------|

|                                                  |         | Inp         | ut Chara     | cteristic  | S     |                                   |

| Input Forward Voltage                            | VF      | 1.6         | 2.0          | 2.4        | V     | IF=10mA                           |

| Input Forward Voltage<br>Temperature Coefficient | ΔVF/ ΔΤ | -           | -1.237       | -          | mV/°C | IF=10mA                           |

| Input Reverse Voltage                            | BVR     | 5           | -            | -          | V     | IR = 10μA                         |

| Input Threshold Current (Low to High)            | IFLH    | -           | 0.25         | 1.5        | mA    | VCC = 30 V, VO< 5V                |

| Input Threshold Voltage<br>(High to Low)         | VFHL    | 0.8         | -            | -          | ٧     | VCC = 30 V, VO> 5V                |

| Input Capacitance<br>(Note 6)                    | CIN     | -           | 60           | -          | рF    | f = 1 MHz, VF = 0 V               |

|                                                  |         | Outp        | out Char     | acteristic | s     |                                   |

| High Level Supply Current                        | ICCH    | -           | -            | 3.0        | mA    | VCC = 5.5 V, VF = 0V, IO = 0 mA   |

| riigii Level 30ppiy Colletti                     | ICCII   |             | 1.9          | 3.0        |       | VCC = 30 V, VF = 0V, IO = 0 mA    |

| Low Level Supply Current                         | ICCL    | -           | -            | 3.0        | mA    | VCC = 5.5 V, IF = 5 mA, IO = 0 mA |

| LOW LOVE SUPPLY CONTENT                          | ICCL    |             | 2.0          | 3.0        |       | VCC = 30 V, IF = 5 mA, IO = 0 mA  |

| High level output current                        |         | -           | -            | -100       |       | VCC = 5.5V, VF = 0V , VO = GND    |

| (Note 7)                                         | IOH     | 1           | -            | -200       | mA    | VCC = 20V, VF = 0V, VO = GND      |

| Low level output current                         |         | 100         | -            | -          |       | VO =VCC = 5.5V, IF = 5mA          |

| (Note 7)                                         | IOL     | 200         | -            | -          | mA    | VO =VCC = 20V, IF = 5mA           |

| High level output voltage                        | VOH     | VCC-<br>0.5 | VCC-<br>0.05 | -          | V     | IOL = -6.5mA                      |

| Low level output voltage                         | VOL     | -           | 0.09         | 0.5        | ٧     | IOL = 6.5mA                       |

Note 6: Input capacitance is measured between pin 1 and pin 3.

Note 7: Duration of output short circuit time should not exceed 10  $\mu s$ .

#### **Switching Specification**

All Typical values at TA = 25°C, unless otherwise specified; all minimum and maximum specifications are at recommended operating condition.

| Parameter                                                          | Symbol                                        | Min. | Тур. | Max. | Unit  | Test Condition                                                                                  |    |       |                  |

|--------------------------------------------------------------------|-----------------------------------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------|----|-------|------------------|

| Propagation Delay Time to<br>Output High Level<br>(Note 8)         | t <sub>PLH</sub>                              | -    | 110  | 220  |       |                                                                                                 |    |       |                  |

| Propagation Delay Time to<br>Output Low Level<br>(Note 8)          | † <sub>PHL</sub>                              | -    | 90   | 220  | ns    | f = 10kHz.                                                                                      |    |       |                  |

| Pulse Width Distortion (Note 9)                                    | PWD                                           | -    | 20   | 120  |       | ns                                                                                              | ns | ns Du | Duty Cycle = 50% |

| Propagation Delay Difference<br>Between Any Two Parts<br>(Note 10) | PDD<br>(† <sub>PHL</sub> - † <sub>PLH</sub> ) | -200 | ı    | +200 |       | V <sub>CC</sub> = 30V                                                                           |    |       |                  |

| Output Rise Time (10 to 90%)                                       | † <sub>r</sub>                                | -    | 6    | -    |       |                                                                                                 |    |       |                  |

| Output Fall Time (90 to 10%)                                       | † <sub>f</sub>                                | -    | 7    | -    |       |                                                                                                 |    |       |                  |

| Common mode transient immunity at high level output (Note 11)      | CM+                                           | 20   | -    | -    | kV/μs | V <sub>F</sub> =0 V V <sub>CC</sub> = 5V,<br>T <sub>A</sub> = 25 °C,<br>V <sub>CM</sub> = 1.5KV |    |       |                  |

| Common mode transient immunity at low level output (Note 11)       | CML                                           | 20   | -    | -    | kV/µs | I <sub>F</sub> =4mA V <sub>CC</sub> = 5V,<br>T <sub>A</sub> = 25 °C,<br>V <sub>CM</sub> = 1.5KV |    |       |                  |

Note 8: The tPLH propagation delay is measured from the 50% point on the leading edge of the input pulse to the 1.3 V point on the leading edge of the output pulse. The tPHL propagation delay is measured from the 50% point on the trailing edge of the input pulse to the 1.3 V point on the trailing edge of the output pulse.

Note 9 Pulse Width Distortion (PWD) is defined as | tPHL - tPLH | for any given device.

Note 10: The difference of tPLH and tPHL between any two devices under the same test condition.

Note 11: CMH is the maximum slew rate of the common mode voltage that can be sustained with the output voltage in the logic high state, VO > 2.0 V. CML is the maximum slew rate of the common mode voltage that can be sustained with the output voltage in the logic low state, VO < 0.8 V. Note: Equal value split resistors (Rin/2) must be used at both ends of the LED.

#### Isolation characteristic

All Typical values at  $T_A = 25$ °C and  $V_{CC} - V_{SS} = 30$  V, unless otherwise specified; all minimum and maximum specifications are at recommended operating condition.

| Parameter                               | Symbol           | Device      | Min. | Тур.             | Max. | Unit | Test Condition                                     |

|-----------------------------------------|------------------|-------------|------|------------------|------|------|----------------------------------------------------|

| Withstand Insulation<br>Test Voltage    | V <sub>ISO</sub> | EMD2A481-SK | 5000 | -                | -    | V    | RH ≤ 40%-60%,<br>t = 1 min, T <sub>A</sub> = 25 °C |

| (Note 12, 13)                           |                  | EMD2A481-SL |      |                  |      |      | 1 = 1111111111111111111111111111111111             |

| Input-Output<br>Resistance<br>(Note 12) | R <sub>I-O</sub> | -           | ı    | 10 <sup>12</sup> | ı    | Ω    | V <sub>I-O</sub> = 500V DC                         |

Note 12: Device is considered a two terminal device: pins 1, 2, 3 are shorted together and pins 4, 5, 6 are shorted together.

Note 13: According to UL1577, each photo coupler is tested by applying an insulation test voltage 6000VRMS for one second.

Publication Date: Mar. 2024

Revision: 1.0 6/12

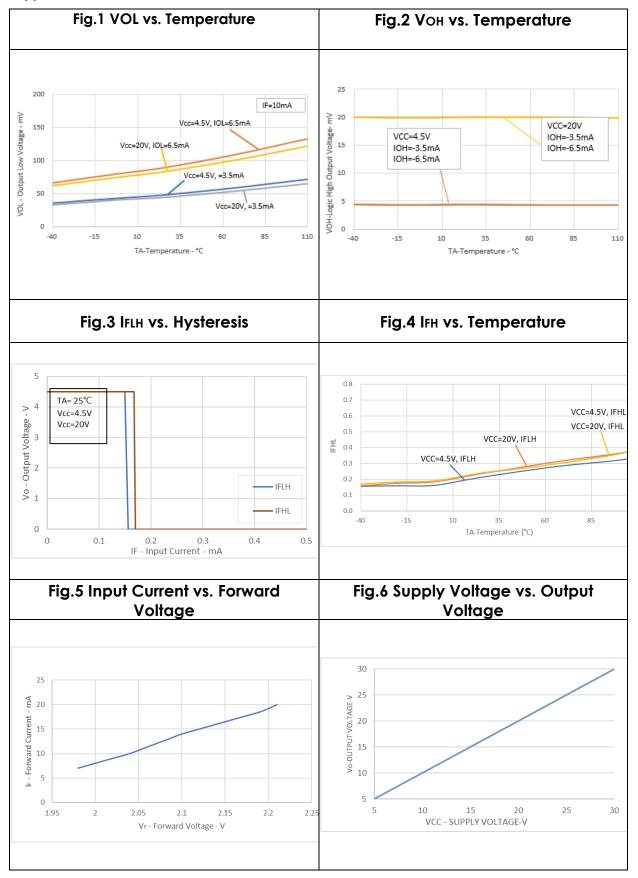

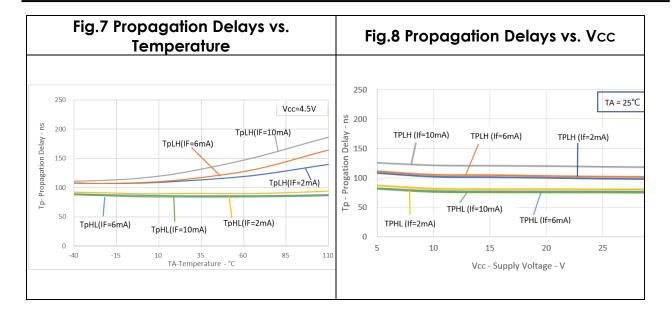

## **Typical Performance Curves & Test Circuits**

Publication Date: Mar. 2024 Revision: 1.0 7/12

Publication Date: Mar. 2024 Revision: 1.0 **8/12**

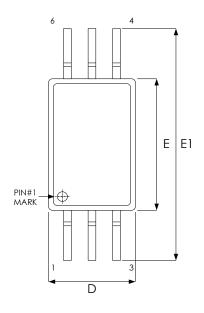

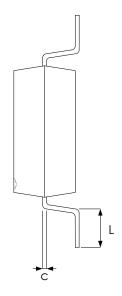

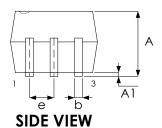

## Package Outline Drawing L-SOP 6L (277mil, 7mm clearance)

**TOP VIEW**

**SIDE VIEW**

| Symbol   | Dimension in mm |       |  |  |

|----------|-----------------|-------|--|--|

| Syllibol | Min.            | Max.  |  |  |

| А        | 1.70            | 2.30  |  |  |

| A1       | 0.10            | 0.30  |  |  |

| ь        | 0.30            | 0.50  |  |  |

| С        | 0.20            | 0.30  |  |  |

| D        | 4.20            | 4.80  |  |  |

| Е        | 6.51            | 7.11  |  |  |

| E1       | 9.40            | 10.00 |  |  |

| е        | 1.27 BSC        |       |  |  |

| L        | 0.70            | 1.20  |  |  |

Publication Date: Mar. 2024 Revision: 1.0 9/12

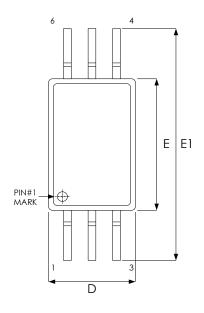

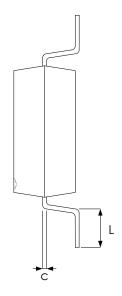

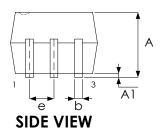

## Package Outline Drawing L-SOP 6L (277mil, 8mm clearance)

**TOP VIEW**

**SIDE VIEW**

| Cymbol | Dimension in mm |       |  |  |

|--------|-----------------|-------|--|--|

| Symbol | Min.            | Max.  |  |  |

| А      | 1.70            | 2.30  |  |  |

| A1     | 0.10            | 0.30  |  |  |

| b      | 0.30            | 0.50  |  |  |

| С      | 0.20            | 0.30  |  |  |

| D      | 4.20            | 4.80  |  |  |

| Е      | 6.51            | 7.11  |  |  |

| E1     | 11.20           | 11.80 |  |  |

| е      | 1.27 BSC        |       |  |  |

| L      | 0.50            | 1.00  |  |  |

Publication Date: Mar. 2024 Revision: 1.0 10/12

# **Revision History**

| Revision | Date       | Description                                                                                                      |

|----------|------------|------------------------------------------------------------------------------------------------------------------|

| 0.1      | 2023.02.17 | Preliminary version                                                                                              |

| 0.2      | 2023.08.24 | Update: Insulation Characteristics (Page3) AMR unit (Page4) Note7 (Page5)   CMH     CML   Test condition (Page6) |

| 1.0      | 2024.03.05 | 1.Revise IOH/IOL spec 2.Update POD 3. Remove "preliminary" to V1.0                                               |

Publication Date: Mar. 2024 Revision: 1.0 11/12

## Important Notice

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.

Publication Date: Mar. 2024 Revision: 1.0 12/12